In a packed session at IDF 2015 in San Francisco last week, Scott Graham, Micron’s general manager of Hybrid Memory, discussed some of the key themes occurring in the memory landscape from Micron’s perspective.

“It’s an exciting time in the industry and there’s a lot going on with memory development in system architecture and software architecture and how they combine together to provide system solutions in the server, mobile computing and embedded and networking environments,” he offered as prelude.

Noting that Micron has a portfolio that spans across platforms and sectors, Graham asked the primarily developer audience to consider how they can use these new and existing memory technologies to develop platforms to solve complex challenges out in the industry.

As the focus in computing moves from the compute bottleneck to the data bottleneck with the slow down of Moore’s law and the proliferation of data, memory and storage technologies are more important than ever. And while HPC certainly has some unique challenges and specific requirements, many concerns related to price, performance and system balance are shared across the larger computing market.

Memory is more diversified than ever and Micron has several technologies and products that are optimized for power and performance and target HPC, including Hybrid Memory Cube, solid state drives, NVDIMMs, 3D NAND, and most recently 3D XPoint, which it developed with partner Intel. The non-volatile memory process technology, unveiled last month, is being heralded by its backers as the first new memory category since the introduction of NAND flash in 1989.

3D XPoint, said Graham, previewing content to come later in his presentation, delivers 1000X the performance of regular multi-level cell (MLC) NAND and 10X higher density than a conventional volatile memory, such as DRAM.

The Update

Graham went on to deliver a technology update for the four key technologies that undergird Micron’s portfolio: DRAM, NAND, package technology (aka Hybrid Memory Cube), and new memory technology (aka 3D XPoint).

In terms of DRAM, Graham said the product continues to come along nicely with strong progress for 20nm yield. And Micron has 1Xnm development underway in Asia and 1Y/1Znm in the US.

For NAND, 16nm TLC NAND is also ramping up, but Micron will be focusing their efforts more on 3D NAND. First generation 3D NAND is on track for production now, and Micron will move to second generation next year.

Micron notes its 3D packaging technology, which has been productized in the HMC line, continues to mature. The company is currently manufacturing HMC generation 2, and will be launching HMC generation 3 over the next year to enable even higher density and bandwidth. Graham reviewed that on the networking side, it is being used in data packet processing and in data packet buffering and storage applications. For the high performance computing space, HMC is used for very high-speed, high-bandwidth technology transactions.

“To be frank, we cannot achieve the applications and system needs without developing a really good packaging technology,” said Graham. “We’re not going to achieve these bandwidth capabilities. We’re not going to achieve the reliability needs. We’re not going to overcome some of the scaling challenges without developing some of these new technology methods. If you look at Hybrid Memory Cube, that’s been the lead vehicle for Micron in order to develop these package technologies for future emerging memories.”

Graham went on to review the benefits of Micron’s in-package memory, stating that it helps to achieve bandwidth, efficiency and form factor all in one package. “If we have the ability to take DRAM and stack it on top of a logic layer and SoC and be able to control that DRAM with that SoC, it allows us to overcome scaling challenges. Being able to combine these technologies together, gives us unprecedented memory bandwidth that keeps pace with multiple CPU cores, and DRAM alone is not going to do that. This all allows for increased savings in energy/bit, density in a small form factor, higher performance and lower energy, and compelling RAS features,” Graham continued.

Challenges to the Longevity of DRAM

Graham also spoke about the impacts of DRAM process complexity, noting that as the industry scales from 50nm to 30nm and then to 20nm, complexity drives really significant upticks in the number of mask levels, by over 35 percent. The number of non-litho steps per critical mask level is up a staggering 110 percent, going from 30nm to 20nm. Clean room space per wafer output is up over 80 percent. Since acquiring Elpida in 2013, Micron says is is getting ahead of its original plan on hitting the 20nm yield. Keeping cost per bit down is a key goal and Micron believes it can enable this by facilitating the scaling path to sub-15nm DRAM. Specifically, Graham noted 1Xnm is driving over a 30 percent improvement in cost per Gb over 20nm.

DRAM is still the primary memory inside nearly every computer, from mobile phones to datacenter servers to supercomputers. But with scaling challenges, improvements have already started slowing. There are also power concerns with DRAM main memory systems accounting for about 30-50 percent of a node’s overall power consumption. These points are all highlighted in a recent journal article written by authors Jeffrey S. Vetter and Sparsh Mittal (of Oak Ridge National Laboratory). The duo then set out to examine what the future might hold for non-volatile memory systems in extreme-scale high performance computing systems.

“For DRAM, there are possible improvements from redesigning and optimizing DRAM protocols, moving DRAM closer to processors, and improved manufacturing processes,” they write. “In fact, this integration of memory onto the package in future systems may provide for performance and power benefits of about one order of magnitude [5]. Second, emerging memory technologies with different characteristics could replace or complement DRAM [13, 15, 19, 24].”

In another part of the paper, Vetter and Mittal write: “Moreover, as the benefits of device scaling for DRAM memory slow, it will become increasingly difficult to keep memory capacities balanced with increasing computational rates offered by next-generation processors. However, a number of emerging memory technologies — nonvolatile memory (NVM) devices – are being investigated as an alternative for DRAM. Moving forward, these NVM devices may offer a number of solutions for HPC architectures. First, as the name, NVM, implies, these devices retain state without continuous power, which can, in turn, reduce power costs. Second, certain NVM devices can be as dense as DRAM, facilitating more memory capacity in the same physical volume. Finally, NVM, such as contemporary NAND flash memory, can be less expensive than DRAM in terms of cost per bit. Taken together, these benefits can provide opportunities for revolutionizing the design of extreme-scale HPC systems.” The full paper fleshes out each of these potential technology trends.

Micron’s General Manager of Hybrid Memory echos many of the same concerns as he discusses Micron’s outlook to the future of memory. “As we look at the future, in order to overcome the scaling challenges, specifically related to DRAM, we need to either find a better DRAM or some type of DRAM replacement,” says Graham. “So we continue to have a strong strategic investment in our roadmap enablement for storage-class memory as well as some type of DRAM or NAND replacement as well as multiple generations of 3D NAND. The strategic investment in the future of those core technologies that we’re looking at today and will continue to invest research dollars in are both resistive RAM as well as SST RAM. And SST-RAM — spin-torque magnetic random-access memory RAM — we think that that technology has a really promising opportunity to perhaps replace DRAM. So it’s DRAM-like but with non-volatile capability. As we continue to explore other opportunities, we will update the community.”

Micron’s condensed roadmap of technologies is shown below:

Emerging Memory and 3D-XPoint

When it comes to Micron’s emerging memory line, not surprisingly the focus is on 3D-XPoint with generation one sampling this year (although first deliveries are not promised until 2016) and a subsequent technology coming the following year. You can also see New Memory B Gen 1 positioned just a little farther out. At first all Graham would say is that “we are working on it now and it will be disclosed at a later date,” but he later confirmed that Micron’s first generation offering would be cost-optimized, while the emerging “new memory B” technology would be focused on performance and addressing some of the bigger industry challenges.

“As we develop new memory technologies and learn from XPoint and develop XPoint even further, then we will have subsequent versions of this technology and other technologies that can fit into this roadmap,” said Graham, declining to provide further details.

This slide gives a idea of where these new memories come down in terms of performance versus cost in relation to DRAM and NAND.

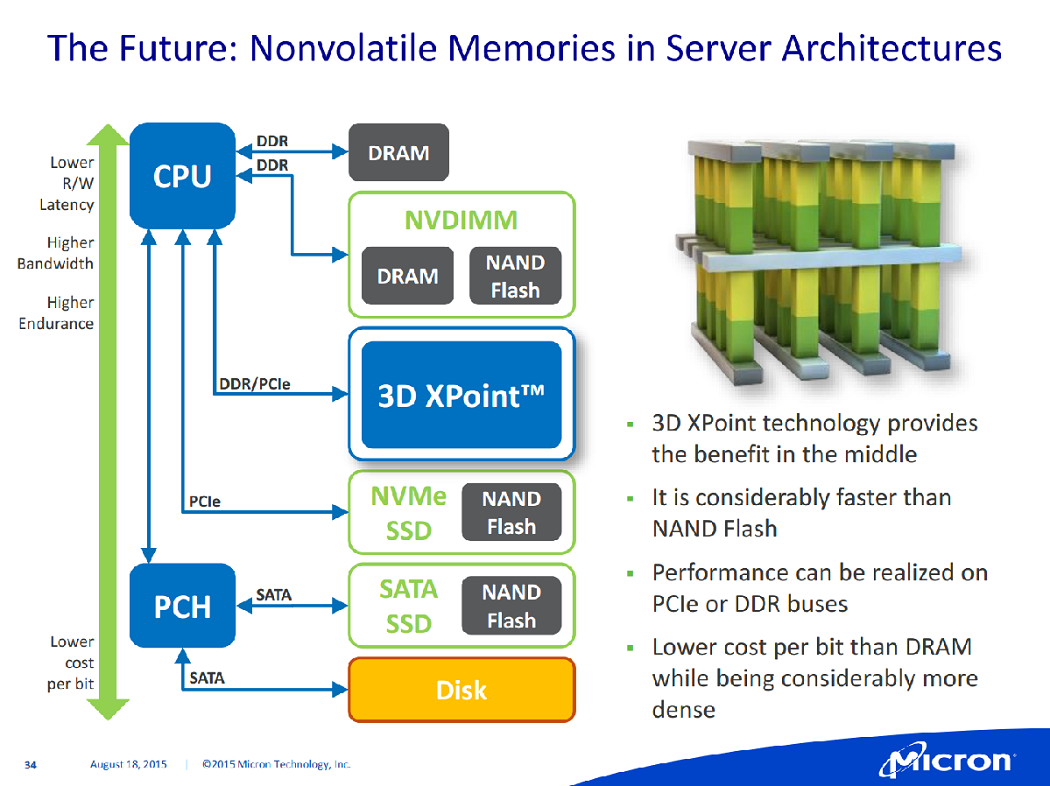

Nonvolatile memory latency is the major challenge of emerging memory in Micron’s view. As CPU technology continues to scale, memory IO continues to experience significant performance bottlenecks, so emerging memory products need to fulfill that huge latency gap. The gap continues to widen with the progression of technologies from DDR2 to DDR3 and DDR4.

Micron and Intel developed 3D XPoint to bridge this gap. As such 3D-XPoint is not intended as a replacement for DRAM or SSD (at least that’s Micron’s view) but for a target niche of applications that include in-memory database, metadata storage as well as application logging and others in verticals such as oil & gas exploration, big data analytics, financial transactions and medical research.

Graham refers to 3D-XPoint as an emerging storage class memory technology that offers DRAM-like performance with higher density and lower energy, and non-volatility with fraction of DRAM cost/bit. It is also said to be 1000x faster than NAND and the performance can be realized on PCIe or DDR buses, but there is concern about the new memory interface being proprietary. For example, Intel’s first go-to-market product, Optane, which slots inside a DDR4, is electrically compatible but will require new CPU and new extensions to access 3D XPoint. Micron has yet to reveal its first XPoint-based product, but said it would be announcing its product plans over the next couple of months.

Micron says it has multiple technologies currently in development and showing promise around XPoint and it realizes the importance of broad industry support to make an emerging memory technology successful. Further development is still needed around controller technology, which is critical to exploit characteristics of each type of memory, as well as software that is capable of taking advantage of the persistent memory semantics.

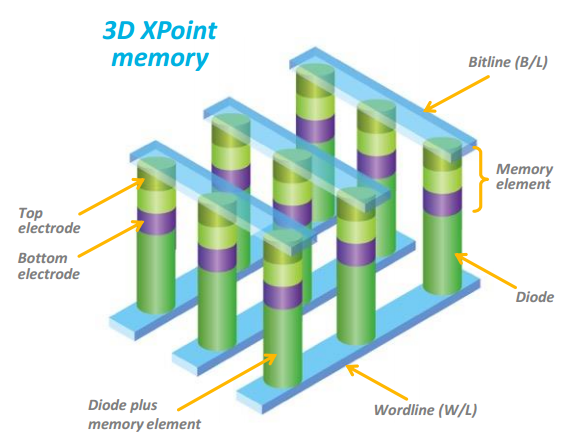

For the record, Micron and Intel still aren’t saying exactly what XPoint is made of, except to reiterate that the memory element plus diode are positioned at the intersection of word and bit lines. The “memory grid” 3-D checkerboard structure maximizes cell density and allows memory cells to be addressed individually.

For the record, Micron and Intel still aren’t saying exactly what XPoint is made of, except to reiterate that the memory element plus diode are positioned at the intersection of word and bit lines. The “memory grid” 3-D checkerboard structure maximizes cell density and allows memory cells to be addressed individually.

Micron looks at memory in a different way now, according to Graham, which is in three buckets: near, bulk and far memory. This is of course the same trend in HPC with increasing attention being paid to memory hierarchies.